# **Advanced Interconnect Test Tool (AITT)**

Versatile Tool for Interconnect Analysis and PCB Characterization

## **AITT Overview**

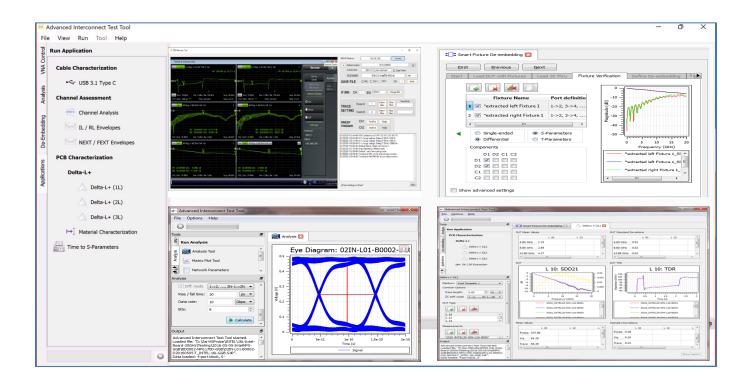

The Advanced Interconnect Test Tool (AITT) is ideal for signal-integrity and power-integrity applications. The AITT software includes the key features: de-embedding, applications including PCB material extraction, analysis tools, and VNA control. It can be installed on a VNA directly or a PC that controls the VNA remotely.

The Advanced Interconnect Test Tool (AITT) is developed by an experienced research team led by two IEEE Fellows in the Missouri S&T EMC Laboratory. This versatile, easy-to-use AITT software has been used by many Fortune 100 companies.

#### **Part Numbers:**

**AITT-AN**: Analysis Tool

**AITT-SFD**: Analysis Tool and Smart Fixture

De-embedding Tool

**AITT-DLP**: Analysis Tool and Delta-L+ Tool

**AITT-ME**: Analysis Tool and Material Extraction

Tool (DK, DF, and surface roughness)

### Features:

- Smart Fixture De-embedding: multiport fixture de-embedding tool supports 2X thru and 1X reflect techniques with superior accuracy.

- Analysis: powerful tool for frequency- domain, time-domain, and eye-diagram analysis, and versatile plotting capabilities.

- Causality/Passivity: tool assesses the causality and passivity of an S-parameter file and can enforce them for non-causal or nonpassive cases.

- VNA Control: control of a VNA locally or remotely by a separate computer.

- Applications:

- PCB Material Extraction tool extracts DK, DF, and surface roughness of PCBs.

- Delta-L 4.0 PCB test tool is based on the Intel Delta-L 4.0 methodology

- Fast C++ runtime with simple installation and script-mode support.

## **Material Characterization (AITT-ME) Tool**

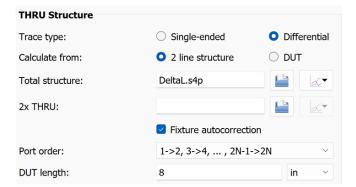

The AITT-ME material extraction tool extracts DK, DF, and surface roughness of a PCB from trace measurements based on the Huray roughness model. DK for both pre-preg and core can be extracted from stripline measurements as well.

The input can be defined as single-ended or differential trace with single or dual mode, or DUT data with 2xThru can be used, where the SFD algorithm will be applied for de-embedding before material extraction. The Intel Extended Unterminated Line (EUL) method is used to extract both core and pre-preg DK.

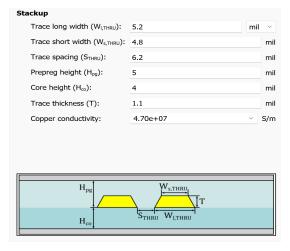

The input stack-up can be developed by putting various geometry parameters, such as trace width, core and pre-preg height, thickness, spacing, and conductivity.

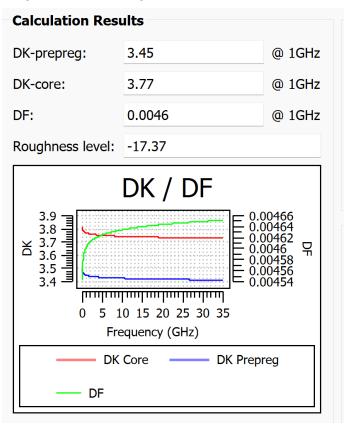

Results for DK pre-preg and core, DF and surface roughness level are given.

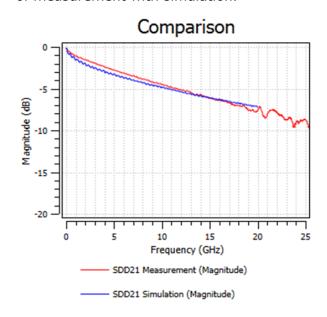

The application gives the common-mode and differential mode insertion losses and comparison of measurement with simulation.